乘法器

此项目仍在支持中,此项目始于2020年

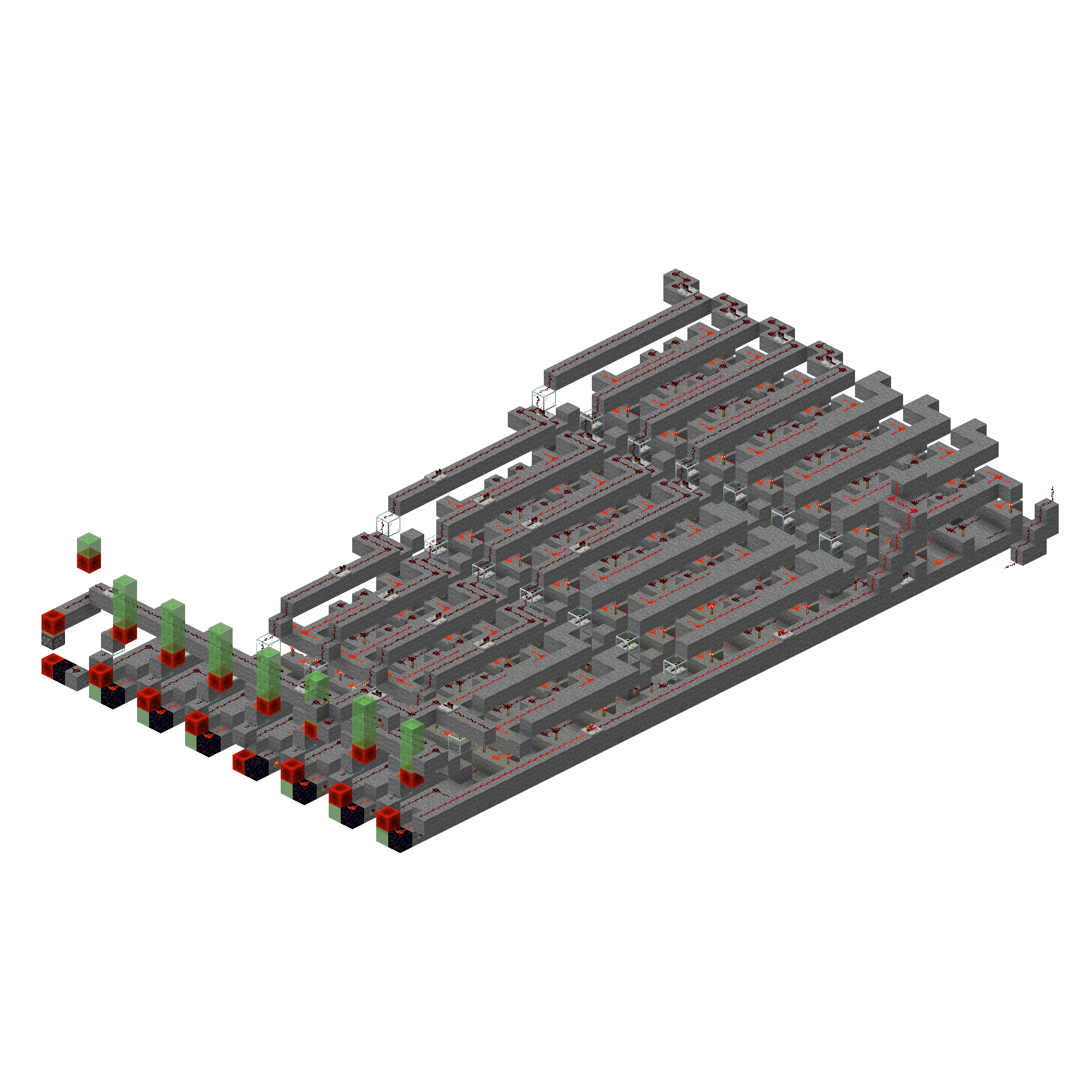

项目当前状态:V1版本已投入使用

乘法器

乘法器是一种完成两个互不相关的模拟信号相乘作用的电子器件。它可以将两个二进制数相乘,它是由更基本的加法器组成的。乘法器可以通过使用一系列计算机算数技术来实现。乘法器不仅作为乘法、除法、乘方和开方等模拟运算的主要基本单元,是一种用途广泛的功能电路。

在实现方法上来说,其主体基于全加器。在运算二进制乘法的过程中,可以发现其一个乘数乘以1得原数,乘以0都得0,此位数乘积完成后,向左移位以计算下一位,当所有位数以此乘积完成后,全部相加得到结果。

在硬件实现上,基于每位乘数MAX=2⁶,结果最大1024,第一级使用5个全加器,并由另一乘数的第一位的1/0来控制是否开启,在第一位为0时,全加器关闭,这一级之前的数(第一级的上一级为“000000”,第N级为第N-1级的结果)通过全加器上方的“跳线”进入下一级输入口,第二级则会接收到向左错位1位的乘数,和上一级经过“跳线”的数。同理由另一乘数的第2位来控制第二级的全加器是否开启,原理同上。

基于这种移位相加的全加器的乘法器主要缺点为体积占用太大,目前的改进方向是缩小其全加器的体积大小,目前最新的全加器可在不改变任何逻辑的情况下:延迟减少0.1s,长度减小4格,宽度不变,高度不变。