ROM

此项目仍在支持中,此项目始于2019年

项目当前状态:V4版本已完成验证

ROM V0.9 (2019.1)(未通过理论验证,已废弃)

作为首个ROM项目,当时的我还没有明确的方向去构造这个模块。这一版本的主要内容为:抛弃穷举的方法,试图从二进制中找到与十进制同一数的关系,主要可使得编码的工作量大大减小。这一项目验证进行了大约12天,正如标题所说,这个项目失败了,没有通过理论验证。在大约半个月后它的正式版本V1才通过验证并推出。

ROM V1 (2019.2)用于MAX=16计算器

此V1项目在吸收V0.9的教训后进行研发,仍然采用穷举的方法。这一代ROM工作于MAX=16计算器中,由于前端ALU的宽度仅为4,所以V1版本没有重视体积以及延迟表现,目标仅为可用。当前V1使用平铺松散式的架构,存储空间为4×15=60bit大小,MIN输出延迟0.3s,MAX输出延迟8.7s。

ROM V1.1 (2019.5)用于MAX=16计算器

相较V1在体积方面V1.1缩减了许多,减少了不必要的中继器带来的延迟,架构、存储空间未改变,MIN输出延迟0.3s,MAX输出延迟4.3s。

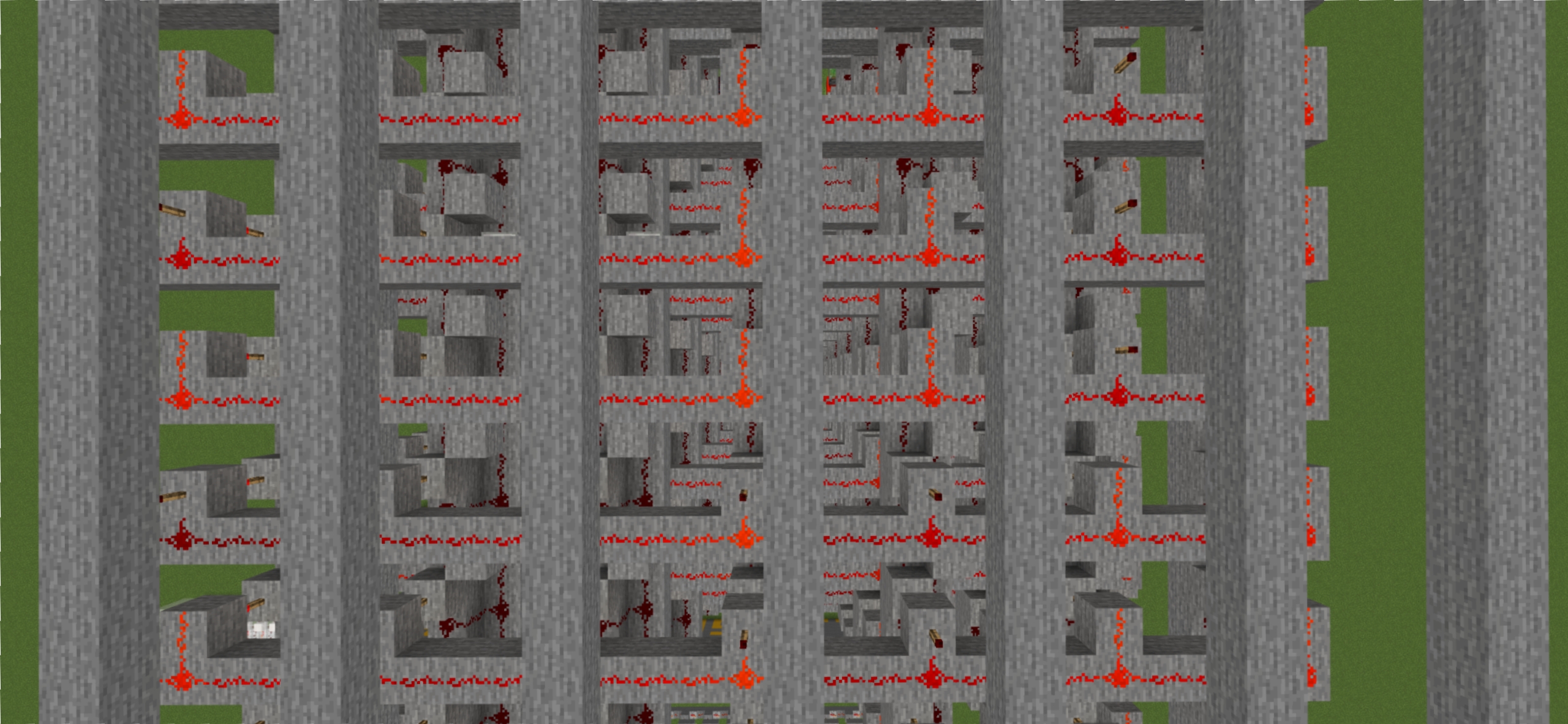

ROM V2 (2019.11)用于MAX=32计算器

计算器前端ALU的宽度加宽至5(MAX=32),故ROM也带来了升级,因为此次ROM需要存储的数据相较V1.1翻倍,进行了较大幅度的架构升级,抛弃平铺式架构,转为3D堆叠式,每一层存储50bit(10个数字xALU宽度),共3层,存储空间至110bit,MIN输出延迟0.3s,MAX输出延迟2.9s。

ROM V2.1 (2019.12)用于MAX=64计算器

计算器前端ALU的宽度继续加宽至6(MAX=64),此次ROM需要存储的数据相较上一代再次翻倍,架构仍为3D堆叠式,更换了输出线路。每一层存储60bit(10个数字xALU宽度),共7层,存储空间至384bit,MIN输出延迟0.3s,MAX输出延迟2.9s。

ROM V2.2 (2021.6)用于MAX=128计算器

本次计算器前端ALU的宽度加宽至7(MAX=128),由于ROM存储格式为每10个数一层,每100个数一组,所以V3版本将为后续升级预留至10宽度,共两组,13层,加入行线列线用于百位输出。每一层存储70bit(10个数字xALU宽度),共13层,存储空间至896bit,MIN输出延迟0.3s,MAX输出延迟1.3s。

ROM V2.3 (2020.7)用于MAX=128计算器

ROM进行小幅度升级,主要为下一次更新做准备,主要为扩宽各输入输出线,优化线路传输延迟。存储空间至896bit,MIN输出延迟0.1s,MAX输出延迟1s。

ROM V3 (2020.9)用于MAX=1024计算器

支持MAX=1024计算器,当前投入使用的最优秀的ROM,正式支持行线列线输出,减小存储数目增加导致的输出延迟的增加斜率。存储空间至896bit,MIN输出延迟0.1s,MAX输出延迟0.9s。

ROM V4 (2020.12)用于MAX=1024 V2计算器 (理论验证阶段)

方案1:继续使用穷举法,合并行线列线,减少延迟,预计MAX输出延迟0.8s。体积继续增大至每一层存储100bit(10个数字xALU宽度),共103层,存储空间至10340bit。

方案2:抛弃穷举法,使用8421转BCD码,不再需要庞大的ROM方案,最大最小输出延迟取决于转码计算速度。(当此方案通过理论验证,则V4方案一则会被取消开发)